#### وزارة التعليم العالى والبحث العلمى

#### Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

جامعة عبدالحميد ابن باديس مستغانم

#### Université Abdelhamid Ibn Badis de Mostaganem

كلية العلوم و التكنولوجيا

Faculté des Sciences et de la Technologie

N°d'ordre: M...../GE/2021

# MEMOIRE DE FIN D'ETUDES DE MASTER ACADEMIQUE

FILIERE: TELECOMMUNICATIONS

Spécialité : Système des Télécommunication

Thème

Etude et Implémentation sur FPGA du protocole I2C: Application au contrôle du codec audio WM8731

#### Présenté par :

- EDDEBI Amira Souhila

- KADDOUR PACHA Hanane

#### Soutenu le 12 / 07/2021 devant le jury composé de :

Président : M. BENTOUMI Mohamed MCB Université de Mostaganem

Examinateur : M. BENBELLA Djelti MCB Université de Mostaganem

Encadreur : M. ABED Mansour MCA Université de Mostaganem

Co-encadreur: M. LARBI BEKlAOUZ Hadj MCB Université de Mostaganem

Année Universitaire : 2020/2021

# Remerciements

Après avoir remercié Dieu Gloire à Dieu

Nous tenons à remercier toutes les personnes qui ont contribué au succès à notre étude et qui nous ont aidés lors de la rédaction de ce mémoire.

Nous voudrons dans un premier temps remercier nos encadreurs de mémoire M.ABED Mansour, et M.BEKLAOUZ LARBI Hadj, qui est aussi notre chef de département de génie électrique, à l'université de Mostaganem pour leurs patience, leurs disponibilité et surtout leurs judicieux conseils, qui ont contribué à alimenter nos réflexions.

Nous remercions également toute l'équipe pédagogique de la Faculté des Sciences et de la Technologie et tout le staff, qui ont contribué de près ou de loin à cette réussite.

Nous tenons à exprimer ma gratitude aux personnes qui m'ont aidé à produire ce mémoire. Ceux qui ont partagé avec nous leur expérience et leurs connaissances dans ce domaine, tout en nos accordaient leur confiance et leur grande indépendance dans l'exécution de missions valorisantes.

## A títre personnel

Nous remercions encore une fois nos familles, pour leur soutien constant et leurs encouragements.

### Enfin

Nous espérons que ce mémoire sera encourageant et bénéfique pour les étudiants des années prochaines, j'espère que vous prendrez plaisir à le lire.

## Je dédie ce travail

A mes chères parents, pour tous leur sacrifices, leur amour, leur tendresse, leur soutien et leur prières tout au long de mes études,

A tous mes chers membres de famílles, pour leur appuí et leur encouragement,

A mes chers professeurs, En raíson de leur sérieux au travail, de leur empressement à nous apprendre et leur encouragement,

Et aussi aux étudiants des années précédentes et prochaines, et j'espère qu'ils seront une référence pour tout développement futur.

**EDDEBI AMIRA SOUHILA**

# Dédicaces

Je dédie ce travail avec beaucoup de remerciements et d'appréciation à :

Ma mère la plus importante personne dans ma vie,

A Mes encadreurs dont j'ai trouvé un grand plaisir à travailler avec : <u>M. Abed Mansour</u> et <u>M. Larbi Beklaouz Hadj</u>

A Mes frères qui ont cru en mes capacités

Et le plus grand dédicace A <u>Anwar Walid</u> qui a eu

un grand rôle dans ce travail

Merci infiniment

KaddourPacha Hanane

#### Résumé

Afin de mettre en œuvre correctement le protocole de communication I2C pour le contrôle des signaux audio, dans ce mémoire, nous avons d'abord commencé par une explication générale et exemples concernant les différents protocoles et normes utilisés dans divers domaines de l'électronique. Après, nous avons discuté le protocole I2C en particulier, en termes de longueur de paquet, transmission de données, adresses et utilisation. Nous avons finalement mis en place un protocole de communication série, dans notre cas, le protocole I2C dans une carte FPGA de référence ALTERA Cyclone II. La première application pratique de cette implémentation est le contrôle du signal sonore.

Pour se faire, nous avons utilisé la carte de développement DE1 comprenant la FPGA ALTERA Cyclone II qui contrôlera le codec audio WM8731 embarqué sur la même carte de développent. Il est à noter que tous les codes sources ont été développés en langage VHDL en utilisant le logiciel Quartus ALTERA V 13.

#### ملخص

من أجل التنفيذ الصحيح لبروتوكول الاتصال I2C للتحكم في الإشارات الصوتية ، بدأنا في هذه المذكرة أولاً بشرح عام و تقديم أمثلة بخصوص البروتوكولات والمعايير المختلفة المستخدمة في مختلف مجالات الإلكترونيات. بعد ذلك، تطرقنا إلى بروتوكول الاتصال I2C على وجه الخصوص، من حيث طول الحزمة ونقل البيانات والعناوين والاستخدامات الممكنة لهذا البروتوكول أخيرًا طبقنا بروتوكول اتصال تسلسلي، في حالتنا، بروتوكول I2C في لوحة رقمية مبرمجة من نوع FPGA البروتوكول. أخيرًا طبقنا بروتوكول تطبيق عملي لهذا التنفيذ المادي هو التحكم في الإشارة الصوتية للقيام بذلك، استخدمنا لوحة التطوير DE1 المحتوية على ALTERA Cyclone II والتي ستتحكم في وحدة ترميز الصوت المدين أن المدين ا

للقيام بدلك، استخدمنا لوحه النطوير DE1 المحتوية على ALTERA Cyclone II والتي ستتحكم في وحدة ترميز الصوت WM8731 المضمن في نفس لوحة التطوير. تجدر الإشارة إلى أنه تم تطوير جميع البرمجيات بلغة VHDL باستخدام برنامج Quartus ALTERA V 13.

#### **Summary**

In order to properly implement the I2C communication protocol for audio signals' control, in this thesis, we have first started with a general explanation and examples concerning different protocols and standards used in various electronics fields. Then, we have discussed the I2C protocol in particular, in terms of packet length, data transmission, addresses and usage. At the end, we have implemented a serial communication protocol, in our case, the I2C protocol in an FPGA card of reference ALTERA Cyclone II. The first practical application of this implementation is the control of the sound signal.

To realize our project, we have used the DE1 development board including the ALTERA Cyclone II FPGA that will control the audio codec WM8731 embedded at the same development board. Note that all source codes have been developed in VHDL language using Quartus ALTERA V 13 software package.

## Liste des abréviations

**ADC** Analog to Digital Converter CAN Control Area Network CCCourant continu **CEC** contrôle entre appareils CEI Commission Electrotechnical International **CPU** Central Processing Unit CSI Camera Serial Interface CTS Clear to send DAC Digital to Analog Converter Data carier detected DCD DDC le signal de synchronisation **DDWG** Digital Display Working Group DSI Display Serial Interface DSR DCE Ready DTR DTE Ready DVD Digital Video Disc DVI dégital vésuel interface **EPROMs** erasable programmable read-only memory FPD-Link Flat Panel Display Link **FPGA** Field Programmable Gate Arrays **GND** Signal Ground **HART** Highway Addressable Remote Transducer **HDMI** High-Definition Multimedia Interface Hi-Fi high fidelity Institute of Electrical and Electronics Engineers IEEE I2C INTER INTEGRATED CIRCUIT IO-Link Inter Out Link ISO International Organization for Standardization LCD Liquid Crystal Display **LED** Light Emitting Diode LHPOUT Left Channel Headphone Output LIN Local interconnect network LLINEIN Left Channel Line Input

i

**LVDS** Low-voltage differential signalling PC ordinateur industriel **PCB** Printed Circuit Board **MIPI** Mobile Industry Processor Interface M-LVDS Multipoint Low-voltage differential signalling **MSB** Most Significant Bit **PCI** Peripheral Component Interconnect PCI E Peripheral Component Interconnect Express **RHPOUT** Right Channel Headphone Output **RLINEIN** Right Channel Line Input **RMS** root mean square RS Recommended Standard RTS Request to send RxReceive data R/W Read/write SAS Serial Attached SCSI **SATA** Serial Advanced Technology Attachment SCL Serial Clock Small Computer System Interface **SCSI SDA** Serial Data SoC **Security Operation Center** SPI Serial Peripheral Interface TCP/IP Transport control protocol/internet protocol Telecommunications Industries Association/Electronic Industries Association TIA/EIA **TMDS** transfert du signal audio et vidéo TTL Transistor transistor logic Tx Transmit data Universal Asynchronous Receiver/Transmitter **UART USB** Universal serial bus **VHDL** VHSIC Hardware Description Language

# Liste des Figures

# Chapitre 1

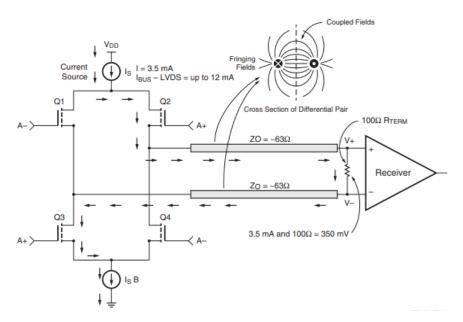

| Figure 1.1 : Liaison LVDS point à point [5].                             | 4  |

|--------------------------------------------------------------------------|----|

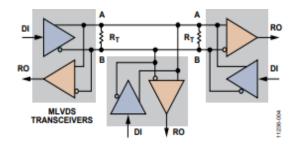

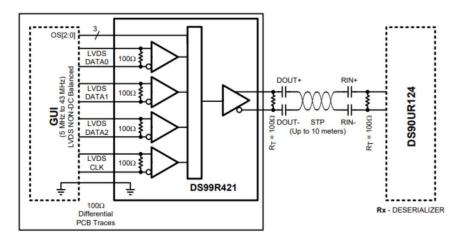

| Figure 1.2: Bus M-LVDS Half-Duplex [4].                                  | 5  |

| Figure 1.3: Bus M-LVDS Full-Duplex[4].                                   | 5  |

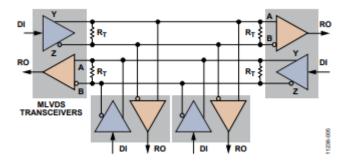

| Figure 1.4: Schéma d'application typique de l'interface FPD-Link [7].    | 5  |

| Figure 1.5 : Bus CAN [9].                                                | 6  |

| Figure 1.6: Formats de trame de message du bus CAN [11].                 | 7  |

| Figure 1.7: Le réseau CAN automobile [12].                               | 8  |

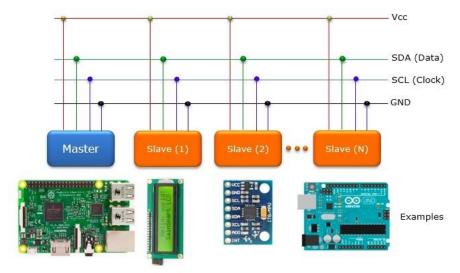

| <b>Figure 1.8:</b> bus I2C [13].                                         | 8  |

| Figure 1.9: Topologie du bus LIN [14].                                   | 9  |

| Figure 1.10: Trame de bus LIN [15].                                      | 9  |

| Figure 1.11 : Exemple d'usage du protocole LIN [16].                     | 9  |

| Figure 1.12: Types de connecteurs DVI femelles [17].                     | 10 |

| Figure 1.13: Trame de donnée du protocole DVI avec FPGA [19].            | 11 |

| Figure 1.14 : Différents types de connecteurs HDMI [22].                 | 11 |

| Figure 1.15 : Prise HDMI [24].                                           | 12 |

| <b>Tableau 1.3</b> : Comparaisons entre les ports Dispaly Port [23].     | 13 |

| Figure 1.16 : Paquet de donnée Display-Port [26].                        | 13 |

| Figure 1.17 : Schéma des connecteurs Display-Port [27].                  | 14 |

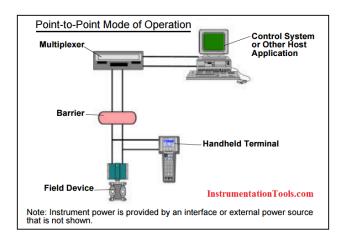

| Figure 1.18: Mode multipoint et point à point configuration réseau [29]. | 14 |

| Figure 1.19: Trame de message HART [30].                                 | 15 |

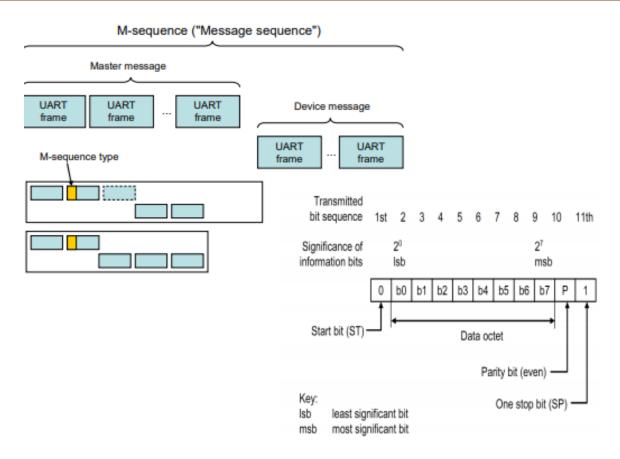

| <b>Figure 1.20</b> : Paquet UART [31].                                   | 16 |

| Figure 1.21 : Schéma bloc d'une architecture PCI [32].                   | 16 |

| Figure 1.22: Exemple de transfert du brust data [34].                    | 17 |

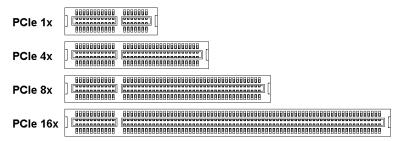

| Figure 1.23: Quatre emplacements du PCIe standard [37].                  | 17 |

| Figure 1.24 : Détection de vitesse USB [38].                             | 18 |

| <b>Figure 1.25 :</b> La trame USB [39].                                  | 18 |

| Figure 1.26 : Schéma fonctionnel d'un appareil mobile typique [41].      | 19 |

| Figure 1.27: Bus CSI du Raspberry PI [42].                               | 19 |

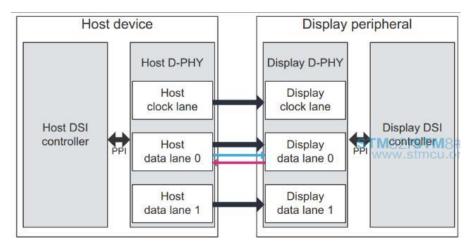

| Figure 1.28: L'interface MIPI-DSI [44].                                  | 20 |

| Figure 1.29: Exemple de l'interface DSI [44].                            | 20 |

| Figure 1.30: Niveau de paquet (paquets courts et longs) [45].            | 20 |

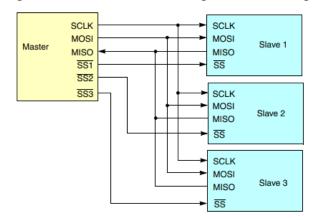

| Figure 1.31: Implémentation SPI maître unique, esclave unique [47].      | 21 |

| Figure 1.32: Mises en œuvre de plusieurs esclaves SPI [47].                                              | 21 |

|----------------------------------------------------------------------------------------------------------|----|

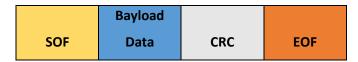

| Figure 1.33 : Trame de donnée SATA [48].                                                                 | 22 |

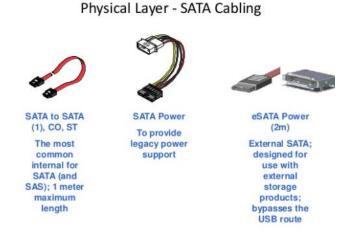

| Figure 1.34: Câbles SATA [48].                                                                           | 22 |

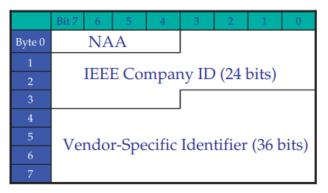

| Figure 1.35: Adresse SAS [51].                                                                           | 23 |

| Figure 1.36 : Séquence de communication maître- Device IO-Link [53].                                     | 24 |

| Figure 1.37: Bus Ethernet [55].                                                                          | 24 |

| Figure 1.38: Paquet Ethernet [54].                                                                       | 24 |

| Figure 1.39 : Le modèle de communication du TCP/IP.                                                      | 25 |

| Chapitre 2                                                                                               |    |

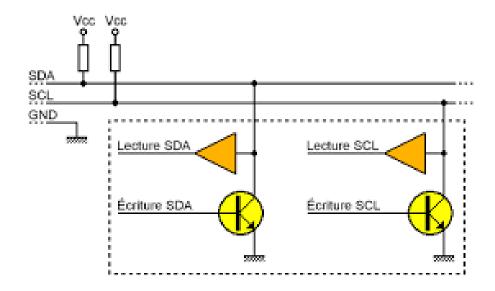

| Figure 2.1 : bus I2C                                                                                     | 27 |

| Figure 2.2 : Structure d'E/S d'un module I2C                                                             | 28 |

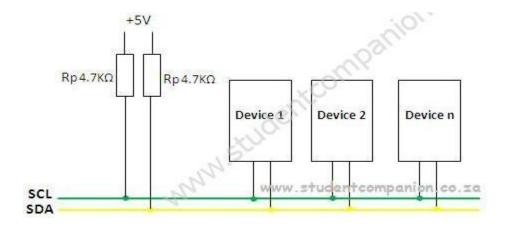

| Figure 2.3 : Câblage I2C                                                                                 | 29 |

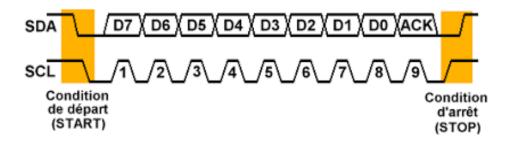

| Figure 2.4 : Condition de départ et d'arrêt                                                              | 29 |

| Figure 2.5 : Exemple de transmission réussie                                                             | 30 |

| Figure 2.6 : Trame de base : Ecriture d un octet                                                         | 31 |

| Figure 2.7: Exemple d'octet d'adresse                                                                    | 32 |

| Figure 2.8 : Exemple de lecture d'une donnée                                                             | 33 |

| Figure 2.9 : Trame de base : Etat d'attente                                                              | 33 |

| Chapitre 3                                                                                               |    |

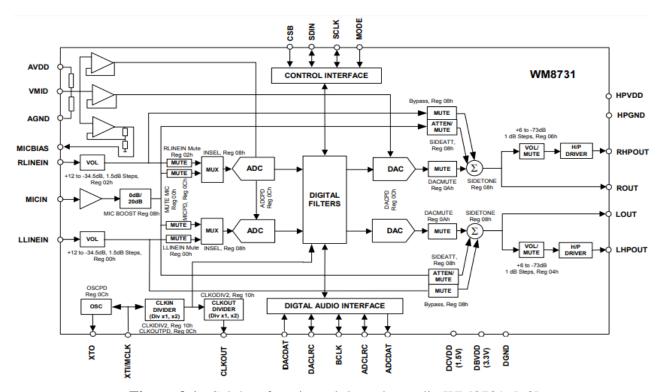

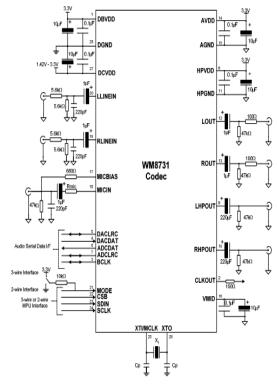

| Figure 3.1 : Schéma fonctionnel du codec audio WM8731.                                                   | 35 |

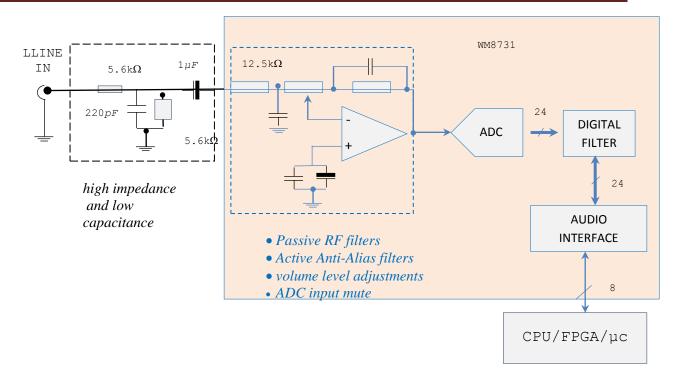

| <b>Figure 3.2:</b> Connexion duWM8731 à un circuit programmable : CPU, FPGA, μcontrôleur                 | 37 |

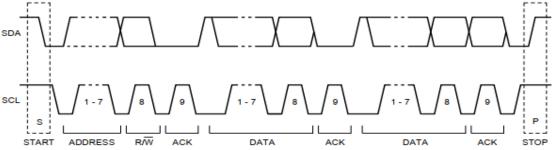

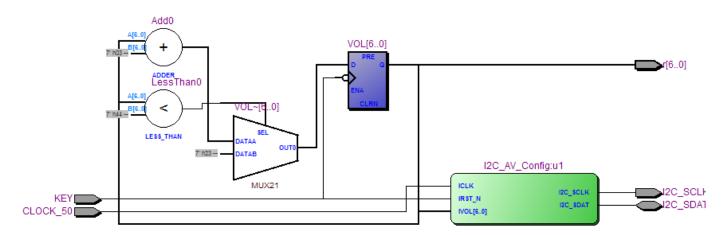

| Figure 3.4 : Contrôleur I2C                                                                              | 38 |

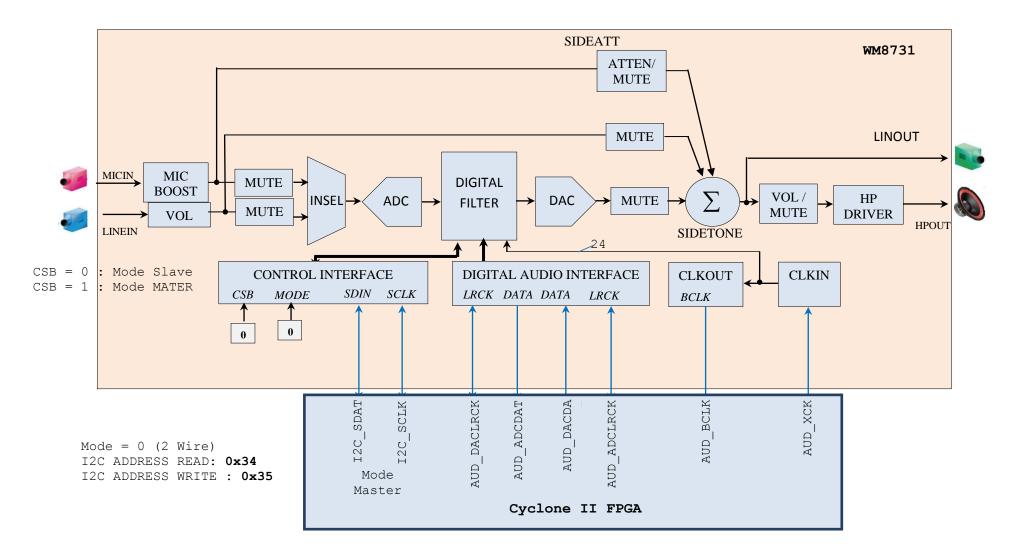

| Figure 3.3: Interface audio numérique avec FPGA Cyclone II                                               | 39 |

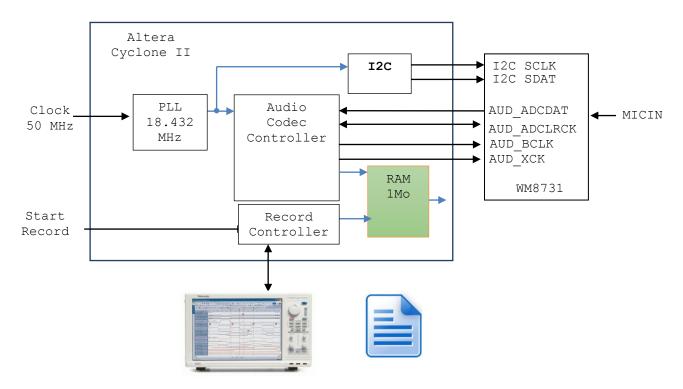

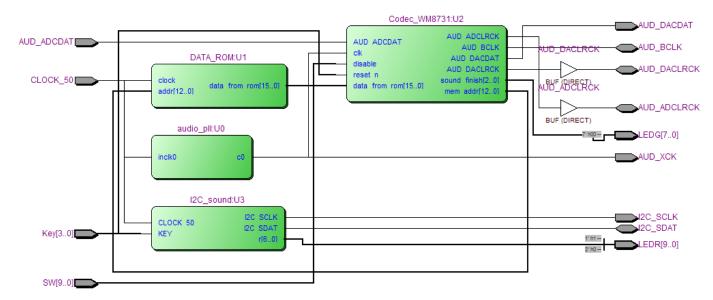

| Figure 3.5 : Configuration matérielle de la méthode de contrôle de son réalisé                           | 40 |

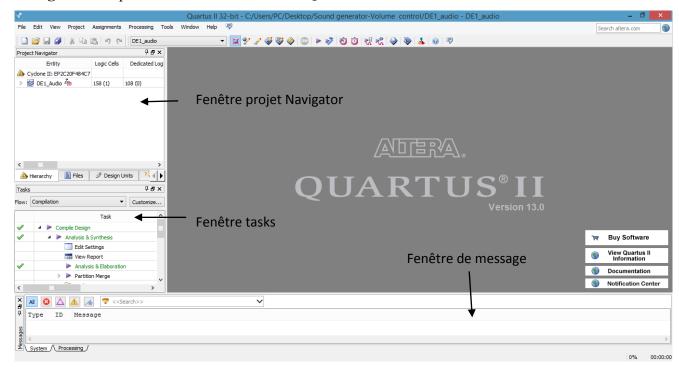

| Figure 3.6 : L'environnement de développement Quartus II.                                                | 41 |

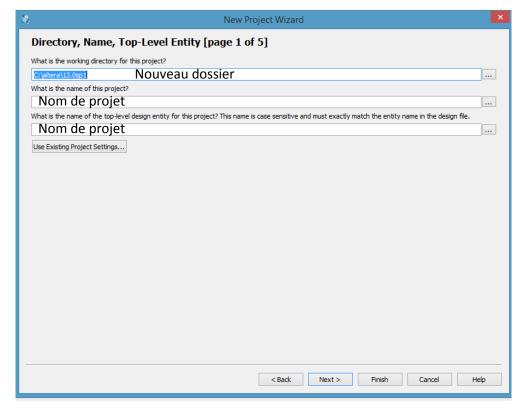

| Figure 3.7 : Création d'un nouveau projet sous Quartus II.                                               | 42 |

| Figure 3.8: Le circuit logique de l'audio_PLL.                                                           | 43 |

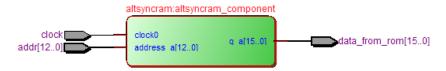

| Figure 3.9: data rom.                                                                                    | 43 |

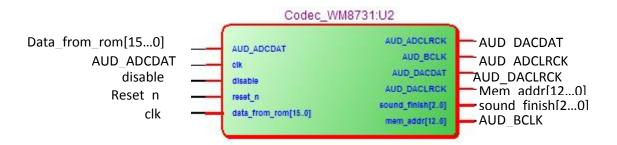

| <b>Figure 3.10</b> : Codec_WM8731.                                                                       | 43 |

| Figure 3.11: Câblage I2C.                                                                                | 44 |

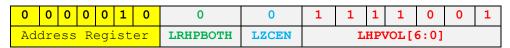

| Figure 3.12 : Adresse du registre LLINEIN.                                                               | 44 |

| Figure 3.13: Schéma global de la FPGA et le codec audio WM8731.                                          | 45 |

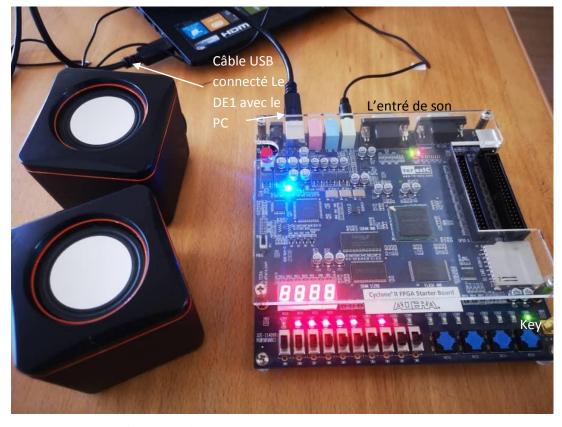

| Figure 3.14 : Photo représentant les manipulations.                                                      | 45 |

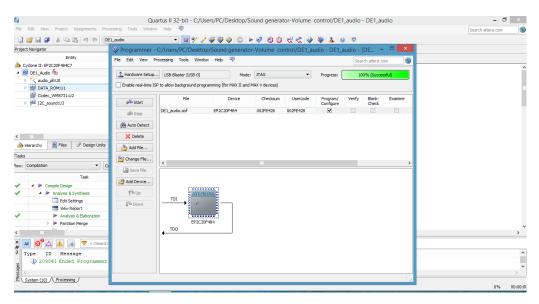

| <b>Figure 3.15:</b> Envois du code source à l'DE1 après montage des différents composants et connectics. | 46 |

# Liste des tableaux

# Chapitre 1

| <b>Tableau 1.1:</b> Comparison entre CAN Low-speed et CAN High-speed [9].                           | 7  |

|-----------------------------------------------------------------------------------------------------|----|

| <b>Tableau 1.2</b> : Comparaisons entre les ports HDMI [23].                                        | 12 |

| <b>Tableau 1.4:</b> Les principales différences entre les interfaces RS-232, RS-422 et RS-485 [32]. | 15 |

| Tableau 1.5 : Caractéristiques du bus PCI [33].                                                     | 16 |

| <b>Tableau 1.6</b> : Vitesses de transmission maximales selon les différentes normes USB [40].      | 18 |

| <b>Tableau 1.7 :</b> Description des signaux [47].                                                  | 21 |

| <b>Tableau 1.8</b> : Taux de liaison physique par direction [50].                                   | 23 |

| Chapitre 2                                                                                          |    |

| Tableau 2.1 : les caractéristique de bus I2C                                                        | 27 |

| <b>Tableau 2.2</b> : Glossaire I2C                                                                  | 28 |

| Chapitre 3                                                                                          |    |

| Tableau 3.1 : Nom, type et description de chaque pin du WM8731                                      | 36 |

| Tableau 3.2: Left and Right Channel Line Input (LLINEIN & RLINEIN).                                 | 44 |

| Tableau 3.3: Left and Right Channel Headphone Output (LHPOUT & RHPOUT).                             | 44 |

# Sommaire

| Liste des abréviations                                                                                                                                                                                                 | i                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Liste des figures                                                                                                                                                                                                      | iii                  |

| Liste des tableaux                                                                                                                                                                                                     | V                    |

| Introduction general                                                                                                                                                                                                   | 1                    |

| Chapitre1: protocoles de communication                                                                                                                                                                                 | 2                    |

| I.1 Introduction                                                                                                                                                                                                       | 3                    |

| I.2 Définition d'un protocole de communication                                                                                                                                                                         | 3                    |

| I.2.1 LVDS (Low-Voltage Differential Signaling)                                                                                                                                                                        | 3                    |

| I.2.2 M-LVDS (Multipoint LVDS)                                                                                                                                                                                         | 4                    |

| I.2.3 FPD-Link (Flat Panel Display Link)                                                                                                                                                                               | 5                    |

| 1.2.4 CAN (Control Area Network) 1.2.5 I2C (INTER INTEGRATED CIRCUIT)                                                                                                                                                  | 6<br>8               |

| I.2.6 LIN (Local interconnect network)                                                                                                                                                                                 | 8                    |

| I.2.7 DVI ( Digital Visuel Interface )                                                                                                                                                                                 | 10                   |

| 1.2.8 HDMI (High-Definition Multimedia Interface)                                                                                                                                                                      | 11                   |

| I.2.9 Display-Port                                                                                                                                                                                                     | 12                   |

| I.2.10 HART (Highway Addressable Remote Transducer)                                                                                                                                                                    | 14                   |

| I.2.11 UART (Universal Asynchronous Receiver/Transmitter)                                                                                                                                                              | 15                   |

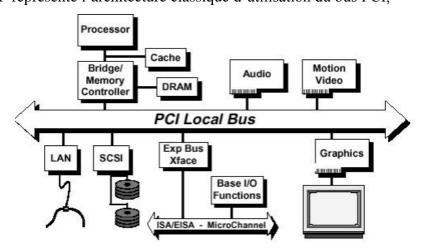

| I.2.12 PCI (Peripheral Component Interconnect) et PCI E (PCI Express)                                                                                                                                                  | 16                   |

| <ul><li>I.2.13 USB (Universal serial bus)</li><li>1.2.14 CSI et DSI</li><li>1.2.15 SPI (Serial Peripheral Interface)</li><li>1.2.16 SAS (Serial Attached SCSI), SATA (Serial Advanced Technology Attachment)</li></ul> | 17<br>18<br>21<br>22 |

| 1.2.17 IO-LINK                                                                                                                                                                                                         | 23                   |

| 1.2.18 Ethernet                                                                                                                                                                                                        | 24                   |

| 1.3 Conclusion                                                                                                                                                                                                         | 25                   |

| Chapitre 2: protocole de communication I2C                                                                                                                                                                             |                      |

| II.1 Introduction                                                                                                                                                                                                      | 26                   |

| II.2 Le bus de communication I2C                                                                                                                                                                                       | 26                   |

| II.2.1 Etude du bus I2C                                                                                                                                                                                                | 27                   |

| II.3 le protocoleI2C                                                                                                                                                                                                   | 28                   |

| II.3.1 Glossaire I2C                                                                                                                                                                                                   | 28                   |

| II.3.2cablage I2C                                                                                                                                                                                                      | 29                   |

| II.3.3La prise de contrôle du bus I2C                                                                                                                                                                                  | 29                   |

# Sommaire

| II.3.4 Ecriture d'un octet (une donnée)                                                                                          | 30             |

|----------------------------------------------------------------------------------------------------------------------------------|----------------|

| II.3.5Transmission d'une adresse                                                                                                 | 31             |

| II.3.6Lecture d'une donnée                                                                                                       | 32             |

| II.4 Utilisation de l'I2C                                                                                                        | 33             |

| II.5 Conclusion                                                                                                                  | 34             |

| Chapitre 3 : Implémentation matérielle du protocole I2C sur ALRETA Cyclone II :<br>Application au contrôle du codec audio WM8731 | •              |

| III.1 Introduction III.2 codec audio et communication I2C III.2.1 Codec audio                                                    | 35<br>35<br>35 |

| III.2.1.1 Description des pins                                                                                                   | 36             |

| III.2.1.2 codec audio et circuit programmable III.2.2 Communication I <sup>2</sup> C                                             | 36<br>38       |

| III.2.3 Adresse de chip WM8731                                                                                                   | 40             |

| III.3 Simulations et implémentations sur FPGA                                                                                    | 40             |

| III.3.1 présentation de Quartus II                                                                                               | 41             |

| II.3.2 Les étapes de simulation                                                                                                  | 42             |

| II.4 Manipulations sur le projet réalisé                                                                                         | 45             |

| III.5 Conclusion                                                                                                                 | 46             |

| Conclusions et <i>recommandations</i> pour les travaux futurs I. Conclusions                                                     | 47             |

| II. Recommandations                                                                                                              | 48             |

|                                                                                                                                  |                |

| Bibliographie                                                                                                                    | 49             |

| Annex                                                                                                                            | <i>-</i> -     |

| Annex A                                                                                                                          | 55             |

| Annex B                                                                                                                          | 72             |

## Introduction générale

Le domaine de télécommunication est couvert de déférentes technologies et disciplines scientifiques. En outre, la communication électronique présente un rôle principal pour évaluer ce domaine. L'objectif est de transmettre des données entre deux ou plusieurs systèmes de telle sorte de reproduire les informations communiquées avec la plus grande fidélité. Pour que les systèmes communiquent entre eux, ils ont besoin d'un ensemble de règles spécifiques à chaque type d'échange de données nommées « protocoles de communication ».

Un protocole de communication peut être défini comme un ensemble de règles standardisées organisant la communication à distance entre systèmes. Cette communication peut s'effectuer en série ou en parallèle ; en mode synchrone ou asynchrone.

La communication série asynchrone signifie qu'un conducteur unique (une seule ligne) est utilisée pour transmettre les données. Si elle est synchrone alors l'acheminement de l'information nécessite l'utilisation de deux lignes : une pour les données et la deuxième pour l'horloge. D'autre part, transmettre l'information bit par bit présente l'avantage de la haute résistance au bruit, la possibilité de communiquer des données sur de longues distances et du coût faible en termes de nombre de fils utilisés.

La communication parallèle, quant à elle, nécessite plusieurs lignes pour transmettre les données sur des paquets de *n* bits à la fois. Son avantage est que la vitesse de transmission est très élevée, bien que sur des distances limitées. Lorsque la distance augmente, la perturbation bruit produite en raison des amplitudes de la ligne de transmission entraîne une déformation du signal reçu en plus du retard dû à la propagation.

Dans notre thème de mémoire, nous allons étudier et implémenter un protocole de communication série, en occurrence, le protocole I2C (Inter Integrated Circuit), dans une carte FPGA. Cette implémentation a pour application d'établir une communication avec le codec audio.

Parmi les différents choix, nous utilisons la carte FPGA de type ALTERA Cyclone II tandis que le codec audio utilisé est de référence WM8731. Ces deux modules sont intégrés sur la carte de développement DE1. Notre objectif principal est de réaliser le circuit électronique du protocole I2C entre la FPGA et le WM8731 sur la carte DE1 programmé avec le langage VHDL de Quartus ALTERA V 13.0. Le cahier de charge consiste à pouvoir contrôler plusieurs paramètres du codec audio à savoir :

- -Volume +/-

- Muter/écouter

- Démarrer/arrêter

Le reste du mémoire est organisé comme suit :

Dans le premier chapitre, nous donnons un aperçu global sur les protocoles de communication les plus utilisés en pratique. Un état de l'art est établi présentant pour chaque protocole étudié sa définition, la structure de son paquet de donnée ainsi que son utilisation pratique,

Le deuxième chapitre est dédié exclusivement au protocole I2C : structure, modes de transmission, câblage, paquets de données ainsi que les avantages et les inconvénients de ce type de protocoles adopté dans ce travail,

Le troisième et le dernier chapitre est réservé au coté pratique, en particulier l'implémentation matérielle du protocole I2C sur ALRETA Cyclone II en utilisant le langage VHDL de Quartus ALTERA V 13.0 en présentant les résultats du contrôle du codec audio conformément au cahier de charge déclaré au début de ce projet.

Ce document est clôturé par des conclusions et des recommandations pour améliorer le présent travail et le développer davantage. Ceci permettra de réaliser des travaux pratiques de haut niveau pour les étudiants de la filière télécommunications, en particulier, en ce qui concerne les technologies et protocoles multimédia. Une annexe est fournie à la fin du document incluant tous les codes sources VHDL utilisés dans l'implémentation proposée.

#### I.1 Introduction

Pour permettre aux deux systèmes de dialoguer entre eux est l'objectif principal de la communication et de l'échange d'informations. Ces deux systèmes doivent parler le même langage, c'est pourquoi nous avons fixé les règles de communication. Toutes ces règles constituent le protocole de communication.

La réalisation du modèle d'échange d'informations ainsi que l'interface de communication des réseaux électriques intelligents dépendent en grande partie du protocole de communication choisi. L'objectif principal de ce chapitre est d'introduire une vue d'ensemble sur les principaux types de ces protocoles ainsi que leurs utilisations pratiques.

#### I.2 Définition d'un protocole de communication

Un protocole de communication est un ensemble de règles qui rendent les communications possibles, car les intervenants sont censés les respecter [1].

Nous avons initialement nommé le protocole celui qui est utilisé pour communiquer sur la même couche d'abstraction entre deux appareils différents. Grâce à l'extension du langage, parfois on utilise aussi ce mot pour préciser les règles de communication entre deux couches sur un même appareil. Il existe plusieurs protocoles et normes de communication, chaque protocole ou norme a des caractéristiques distinctives.

#### **I.2.1 LVDS (Low-Voltage Differential Signaling)**

LVDS est une norme technique qui spécifie les caractéristiques électriques d'une norme de signalisation différentielle et série, mais ce n'est pas un protocole [2]. Le LVDS fonctionne à faible consommation et peut fonctionner à des vitesses très élevées (jusqu'à plusieurs GBit/s [3]) à l'aide de câbles en cuivre (distances allant jusqu'à 10 m [3]) à paires torsadées peu coûteux. LVDS est une spécification de couche physique uniquement. La norme principale pour le LVDS est TIA/EIA-644. Une autre norme parfois utilisée pour LVDS est IEEE 1596.3— SCI [4].

En 1994, Il à été introduit par National Semi-Conductor, qui est devenu un standard réaliste pour la transmission de données à haut débit [5].

Une liaison LVDS point à point, illustrée à la **Figure 1.1**, se compose d'un émetteur de courant générant une chute de tension aux bornes d'une résistance de terminaison (leur valeur est 100Ω) placée du côté récepteur. La tension (égale 350 mV) aux bornes du la résistance de terminaison est proportionnelle au courant d'entraînement (égale 3.5 mA) et permet au récepteur de reconnaître un signal valide [5].

Figure 1.1: Liaison LVDS point à point [5].

Il existe de nombreuses applications dans de nombreux segments de marché qui utilisent LVDS pour la transmission de données telle que téléviseurs LCD, les systèmes d'info-divertissement automobile, les caméras industrielles et la vision industrielle, les ordinateurs portables et tablettes et les systèmes de communication. Les applications typiques sont la vidéo haute vitesse, les graphiques, les transferts de données de caméra vidéo et les bus informatiques à usage général [2].

#### I.2.2 M-LVDS (Multipoint LVDS)

La norme M-LVDS (Standard TIA/EIA-899) est une nouvelle norme qui a été créée en réponse à une demande de la communauté des communications de données pour une norme d'interface équilibrée à haute vitesse à utiliser en général pour les applications multipoints [6].

Elle spécifie les pilotes et les récepteurs de signalisation différentielle basse tension pour l'échange de données à travers structures de bus de données semi-duplex ou multipoint. M-LVDS est capable de fonctionner à des taux de signalisation jusqu'à 500 Mbit/s. [6]

Il existe deux types de multipoints bus, semi-duplex et duplex intégral, illustrés à la **Figure 1.2** et **Figure 1.3**, respectivement. Dans un bus semi-duplex, deux fils sont utilisés de telle sorte qu'un appareil puisse transmettre et que les autres appareils puissent recevoir. Dans un bus full-duplex, quatre fils sont utilisés, permettant à un nœud pour transmettre simultanément à un autre émetteur [4].

Figure 1.2: Bus M-LVDS Half-Duplex [4].

**Figure 1.3**: Bus M-LVDS Full-Duplex[4].

#### I.2.3 FPD-Link (Flat Panel Display Link)

Flat Panel Display (FPD) est un protocole de transmission de flux vidéo numériques des processeurs graphiques vers les écrans numériques. Il s'agit d'une interface interne qui utilise une signalisation différentielle basse tension pour transmettre des paires de bits vidéo sérialisés. Pour ce faire, il sérialise les données TTL parallèles des cartes graphiques. En utilisant trois paires de données et une paire pour l'horloge, le protocole transmet une vidéo RVB 18 bits. Les nouvelles liaisons FPD utilisent quatre paires de données et une paire d'horloges pour transmettre des couleurs 24 bits et 30 bits [7].

Exemple d'application : Le DS99R421 (illustrée à la Figure 1.4) convertit une entrée FPD-Link avec 4 LVDS équilibrés non CC (3 données LVDS + horloge LVDS) plus 3 bits de contrôle basse vitesse suréchantillonnés en un seul flux série LVDS équilibré CC avec des informations d'horloge intégrées. Ce flux série unique simplifie le transfert du bus 24 bits sur une seule paire différentielle de pistes et de câbles PCB en éliminant les problèmes d'asymétrie entre les 3 entrées de données LVDS parallèles et les chemins d'horloge VLDS. Il permet de réduire les coûts du système en réduisant 4 paires LVDS à 1 paire LVDS, ce qui réduit à son tour les couches de circuits imprimés, la largeur du câble, la taille du connecteur et les broches [7].

Figure 1.4: Schéma d'application typique de l'interface FPD-Link [7].

FPD-Link II est une version améliorée de FPD-Link qui a été introduite en 2006. Elle était spécialement conçue pour les applications automobiles et les interfaces de caméra. FPD-Link III était introduite en 2010 pour réduire les câbles. Elle est particulièrement utilisée pour se débarrasser des câbles pour les canaux de contrôle tels que les bus I2C et CAN [8].

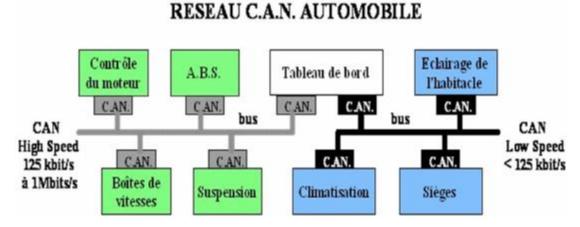

#### 1.2.4 CAN (Control Area Network) [9]

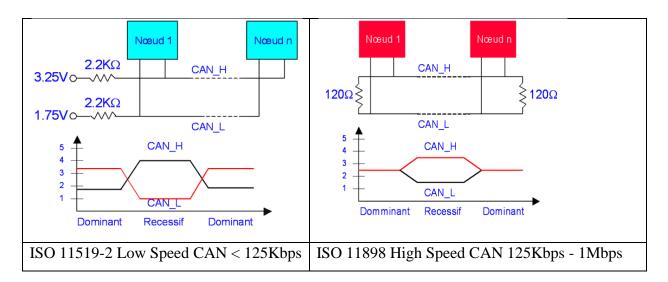

C'est un protocole (réseau) de communication série asynchrone développé par Robert Bosch (fournisseur de système automobile allemand en 1985) [10]. Le CAN était normalisé par la norme ISO11898 pour les applications grandes vitesses et ISO11519 pour les applications basses vitesses. [10]

Le CAN est un bus multi-maitre, chaque système relié avec le bus est appelé un nœud. Ces nœuds sont d'un nombre illimité et sans adresses. Cela signifie que tout les nœuds se considèrent égaux, et donc peuvent tous envoyer en même temps. Pour cette raison, un « filtrage de message » doit être effectué pour déterminer la priorité et les données sur le bus concerné.

La **Figure 1.5** montre que ce bus a deux lignes (le câble contient une pair torsadée blindée ou non blindée) avec une résistance de polarisation II existe deux types de transmission: Low-speed et High-speed.

**Figure 1.5 :** Bus CAN [9].

Les principales différences entre les deux types de bus sont résumées dans le tableau cidessous (**Tableau 1.1**).

| Paramètre                          | CAN Low-speed            | CAN High-speed         |

|------------------------------------|--------------------------|------------------------|

| Débit                              | 125 Kbit/s               | 125 Kbit/s à 1 M bit/s |

| Nombre des nœuds                   | 2 à 20                   | 2 à 30                 |

| Résistance de polarisation         | 2 ,2kΩ                   | 60 Ω                   |

| Courant de sortie en mode émission | 1m A                     | 25 à 50 m A            |

| Niveau dominant                    | CAN H =4V                | CAN H - CAN L = 2V     |

|                                    | CAN L = 1V               |                        |

| Niveau récessive                   | CAN H =1.75V             | CAN H - CAN L = 2.5V   |

|                                    | CAN L = 3.25V            |                        |

| Caractéristique de câble           | 30Pf entre les câbles de | $2 \times 120 \Omega$  |

|                                    | linge                    |                        |

| Tension d'alimentation             | 5 V                      | 5 V                    |

Tableau 1.1: Comparison entre CAN Low-speed et CAN High-speed [9].

Notons que la longueur maximale du câble est de 40 mètre véhiculant un débit de 1 Mbits/s.

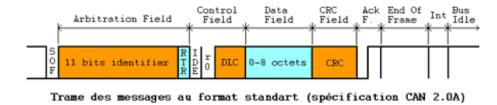

Les données se transférant dans la trame admettent deux formats. La différence réside dans le champ « longueur de l'identificateur » (**Figure 1.6**):

Identificateur à 11 bits: est le format CAN standard, appelé CAN 2.0 A.

Identificateur à 29 bits: est le format CAN étendu, appelé CAN 2.0 B.

Trame des messages au format étendu (spécification CAN 2.0B)

**Figure 1.6 :** Formats de trame de message du bus CAN [11].

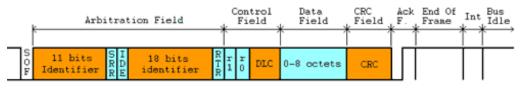

On utilise le protocole CAN dans des applications non-industrielles comme les laboratoires et port automatique ainsi que dans les applications industrielles comme l'escalier mécanique.

**Exemple d'application** : Il est utilisé dans l'automobile pour faire dialoguer les divers systèmes de contrôle ou de commande : ABS, système de freinage, de suspension, etc. [12]

Figure 1.7: Le réseau CAN automobile [12].

#### 1.2.5 I2C (INTER INTEGRATED CIRCUIT)

C'est un protocole de communication série synchrone le plus connu utilisé dans les techniques de processus pour contrôler leurs périphérique.

Il s'agit d'un bus série à deux lignes, l'une pour les données et l'autre pour l'horloge, polarisée par une résistance pull-up dont les valeurs sont comprises entre 2 et  $10~\mathrm{K}\Omega$  avec une charge capacitive 400pF. La **Figure 1.8** représente un exemple de pochage du bus I2C avec de différents systèmes.

**Figure 1.8:** bus I2C [13].

Le lecteur est sollicité à lire le Chapitre 2 pour plus de détails.

#### I.2.6 LIN (Local interconnect network)

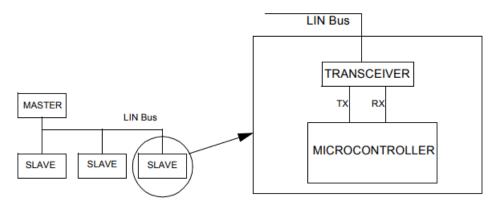

Le LIN est un bus de communication série synchrone présent dans des systèmes distribués pour application automobile. Il contient un seul maitre et plusieurs esclaves.

La **Figure 1.9** présente le brochage des nœuds avec le bus LIN. Ces nœuds se composent typiquement d'un microcontrôleur pour gérer le protocole LIN et d'un émetteur-récepteur LIN pour connecter la partie numérique et la ligne physique [14].

Figure 1.9: Topologie du bus LIN [14].

Les principales caractéristiques du bus LIN sont : Adresse sur 9 bit. Débits : max 20 kbit/s,

Resistance pull-up :  $30K\Omega$  au slave,  $1K\Omega$  au maitre

La Figure 1.10 montre les bits circulés entre les nœuds.

| Sync break field | Sync field   | Protected        | DATA 1          | DATA 2      | DATA N | Checksum |

|------------------|--------------|------------------|-----------------|-------------|--------|----------|

| (14 Bits)        | (10bits)     | identifier filed |                 | (10-80bits) | )      | (10bits) |

|                  |              | (10bits)         |                 |             |        |          |

| N                | Message Head | er               | Message Réponse |             |        |          |

Figure 1.10: Trame de bus LIN [15].

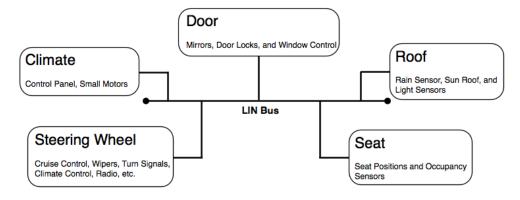

**Exemple :** Il peut être utilisé comme un sous-réseau du bus CAN pour gérer des capteurs comme montré sur la **Figure 1.11**.

Figure 1.11: Exemple d'usage du protocole LIN [16].

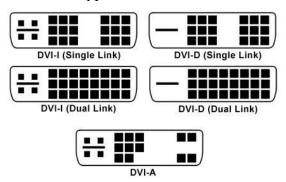

#### **I.2.7 DVI (Digital Visuel Interface)**

C'est une interface visuelle numérique qui a été introduite pour la première fois en 1999 par le groupe de travail sur l'affichage numérique (DDWG). Parmi les avantages du câble DVI on cite [17]:

- 1- Créer une interface informatique standard que tous les écrans et cartes graphiques pourraient partager afin de rationaliser le processus d'installation des ordinateurs, tant pour les entreprises que pour les consommateurs,

- 2- Un câble DVI maximise la qualité des écrans plats LCD.

Le DVI a trois catégories :

- DVI-A: Analogique uniquement (contient 17 pins),

- DVI-D: Numérique uniquement Single Link (Contient 23 pins)

Dual Link (Contient 25 pins)

- DVI-I : Analogique et numérique Single Link (Contient 23 pins)

Dual Link (Contient 29 pins).

La Figure 1.12 présente les différents types de connecteurs selon les catégories.

Figure 1.12: Types de connecteurs DVI femelles [17].

La longueur maximale des câbles DVI n'est pas incluse dans les spécifications car elle dépend de l'horloge des pixels fréquence, et donc les exigences de bande passante du mode vidéo [18]:

- La longueur du câble est d'environ 4.5 m pour la résolution 1920×1080 avec une fréquence de 144 Hz. La bande passante maximale est de 7.44 Gbps.

- La longueur maximale du câble est 15 m pour la résolution d'affichage 1280×1024 avec fréquence d'oscillation 60 Hz.

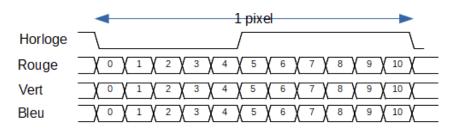

La **Figure 1.13** montre que la trame DVI est envoyée à un appareil pixel par pixel et ligne par ligne. Chaque pixel se constitue de trois composants : rouge, vert et bleu. L'horloge, quant à elle, sert à la synchronisation [19].

Figure 1.13: Trame de donnée du protocole DVI avec FPGA [19].

#### **1.2.8 HDMI (High-Definition Multimedia Interface)**

C'est une norme d'interface utilisée pour l'équipement audiovisuel tel que la télévision haute définition et les systèmes de cinéma maison. Avec 19 fils enveloppés dans un seul câble qui ressemble à un fil USB, HDMI est capable de transporter une bande passante de 5Gbps. C'est plus du double de la bande passante nécessaire pour transmettre l'audio et les vidéo multicanaux [20].

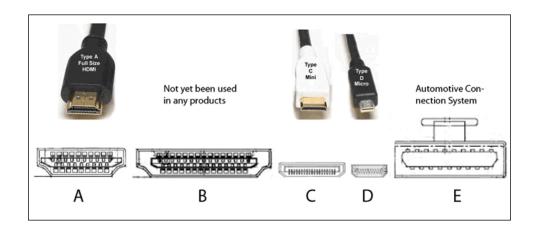

HDMI est capable de transférer de la vidéo, de l'audio et des données non compressés à l'aide d'un seul câble. Les taux de pixels vidéo sont généralement de 25 MHz à 266 MHz (et la vidéo 3D) [21]. La **Figure 1.14** présente déférent types de connecteurs HDMI.

Figure 1.14 : Différents types de connecteurs HDMI [22].

Le tableau ci-dessous (**Tableau 1.2**) donne un aperçu compact sur les méthodes de connexion courantes du protocole HDMI.

|                                                         | HDMI 1.4                               | HDMI 2.0                                | HDMI 2.1                                       |

|---------------------------------------------------------|----------------------------------------|-----------------------------------------|------------------------------------------------|

| Les résolutions les plus<br>importantes                 | 3840 ×2160p -24Hz<br>1920 ×1080p -24Hz | 3840 ×2160p -60Hz<br>1920 ×1080p -144Hz | 7680 ×4320p -60Hz<br>3840 ×2160p -60Hz<br>(3D) |

| Bande passante<br>maximale                              | 10.2 Gbit/s                            | 18 Go/s                                 | 38,4 Gbits/s                                   |

| Transmission du son                                     | Oui                                    | Oui                                     | Oui                                            |

| Transmission 3D                                         | Oui                                    | Oui                                     | Oui                                            |

| Daisy-chaining (plusieurs moniteurs avec un seul câble) | Oui                                    | Oui                                     | Oui                                            |

**Tableau 1.2**: Comparaisons entre les ports HDMI [23].

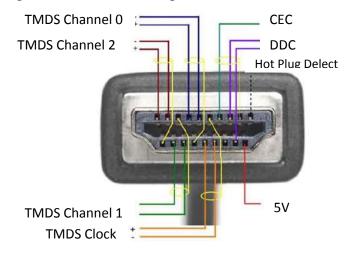

La Figure 1.15 d'une prise HDMI montre les paires différentielles.

**Figure 1.15 :** Prise HDMI [24].

#### I.2.9 Display-Port

Display-Port est une norme industrielle qui s'adapte à l'adoption croissante de la technologie d'affichage numérique dans les PC industriels. Elle fournit une prise en charge des applications pour un débit de canal de liaison allant jusqu'à 21.6 Gbit/s. En outre, elle répond aux besoins à long terme de l'industrie des PC pour prendre en charge des définitions d'image supérieures à 2048×1536 et des profondeurs de couleur supérieures à 24 bits. Elle prend en charge la transmission à bande passante réduite via un entraînement direct sur un câble de 15 mètres. Display-Port prend aussi en charge un minimum de lignes 1080p à 24 bpp, avec des

fréquences d'oscillation verticale de 50 et 60Hz sur 4 voies à 15 mètres [25]. Le **Tableau 1.3** reporte une comparaison entre les ports du Display-Port en termes de caractéristiques.

|                                                         | Display Port 1.1 | Display Port 1.2       | Display Port 1.3 | Display Port 1.4 |

|---------------------------------------------------------|------------------|------------------------|------------------|------------------|

|                                                         |                  |                        | 7680× 4320 –     | 7680 × 4320 –    |

|                                                         | 3840 ×2160p –    | $3840 \times 2160 p -$ | 30 Hz            | 60 Hz            |

| Les résolutions les                                     | 30 Hz            | 60 Hz                  | 3840 ×2160 –     | 3840 ×2160 –     |

| plus importantes                                        | 1920× 1080 –     | 1920 ×1080 –           | 120 Hz           | 120 Hz           |

|                                                         | 144 Hz           | 144 Hz                 | 1920 ×1080 –     | 1920 ×1080 –     |

|                                                         |                  |                        | 144 Hz           | 144 Hz           |

| Bande passante maximale                                 | 8.64 Gbits/s     | 17,28 Gbits/s          | 25.9 Go/s        | 32.4 Go/s        |

| Transmission du son                                     | Oui              | Oui                    | Oui              | Oui              |

| Transmission 3D                                         | Non              | Oui                    | Oui              | Oui              |

| Daisy-chaining (plusieurs moniteurs avec un seul câble) | non              | Oui                    | Oui              | Oui              |

**Tableau 1.3**: Comparaisons entre les ports Dispaly Port [23].

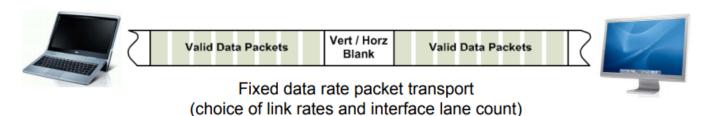

La **Figure 1.16** présente, quant à elle, le paquet de données Display-Port transmis à débit fixe (choix des débits de liaisons et du nombre de voies d'interface). Les connecteurs de type Display-Port sont affichés à la **Figure 1.17**.

Figure 1.16 : Paquet de donnée Display-Port [26].

# CONNECTEUR DISPLAYPORT (20 PIN) CONNECTEUR MINI DISPLAYPORT 7.50 MM PIN #20 PIN #20 PIN #20 CONNECTEUR MINI DISPLAYPORT

Figure 1.17 : Schéma des connecteurs Display-Port [27].

#### I.2.10 HART (Highway Addressable Remote Transducer)

C'est un protocole de communication conçu pour applications de mesure et de contrôle de processus industriels. Appelé un protocole hybride parce qu'il combine la communication analogique et numérique. Ça peut communiquer une seule variable à l'aide d'un signal analogique 4-20 mA. L'information numérique est véhiculée par une modulation de bas niveau superposée à la boucle de courant standard de 4 à 20 mA. Il est très approprié pour une utilisation sur le terrain pour économiser le câble de connexion [28]. Les appareils HART peuvent fonctionner dans l'une des deux configurations de réseau : point à point ou multipoint illustrées à la **Figure 1.18**.

Figure 1.18: Mode multipoint et point à point configuration réseau [29].

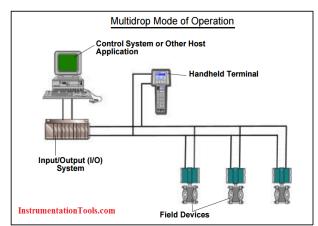

Le format de trame de message HART, souvent appelé télégramme HART, est illustré dans la **Figure 1.19.** Il se compose de neuf champs.

Figure 1.19: Trame de message HART [30].

#### **I.2.11 UART (Universal Asynchronous Receiver/Transmitter)**

L'émetteur- récepteur asynchrone universel est un protocole de communication matériel qui utilise une communication série asynchrone avec une vitesse configurable. Asynchrone signifie qu'il n'y a pas de signal d'horloge pour synchroniser les bits de sortie du dispositif de transmission allant à l'extrémité de réception [31].

Les désignations RS-232, RS-422 et RS-485 font référence aux interfaces pour la transmission de données numériques. Les interfaces RS-422 et RS-485 sont largement utilisées dans l'industrie pour connecter divers équipements. Le **Tableau 1.4** montre les principales différences entre les interfaces RS-232, RS-422 et RS-485

| <b>Tableau 1.4:</b> Les principales différences entre les interfaces RS-232, RS-422 et RS-4 | 85 [32]. |

|---------------------------------------------------------------------------------------------|----------|

|---------------------------------------------------------------------------------------------|----------|

| Nom de port             | RS-232              | RS-422            | RS-485              |

|-------------------------|---------------------|-------------------|---------------------|

|                         |                     |                   | Half-duplex         |

| Type de transfert       | Full-Duplex         | Full-Duplex       | (2 fils)            |

|                         |                     |                   | Ful-duplex (4 fils) |

| Distance maximale       | 15 màtra à 0600hns  | 1200 mètre à      | 1200 mètre à        |

| Distance maximale       | 15 mètre à 9600bps  | 9600bps           | 9600bps             |

| Contact in use          | TxD, RxD, RTS, CTS, | TxA, TxB, RxA,    | Data A, Data B,     |

| Contact in use          | DTR ,DSR, DCD, GND  | RxB, GND          | GND                 |

| Topologie Point à point |                     | Point à point     | Multipoint          |

|                         |                     |                   | 32 (avec un nombre  |

| Nombre d'appareils      | 1                   | 1(10 appareils en | de répéteurs plus   |

| connectés maximal       | 1                   | mode réception)   | élevé généralement  |

|                         |                     |                   | jusqu'à 256)        |

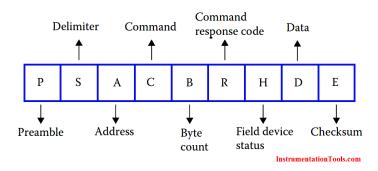

Le mode de transmission est sous forme de paquet. La pièce qui relie l'émetteur et le récepteur inclut la création de paquets série et contrôle ces lignes matérielles physiques. Un paquet se compose d'un bit de départ, d'une trame de données, d'un bit de parité et de bits d'arrêt. Illustrée à la **Figure 1.20** [31].

| Start | Bit | Data frame        | Parity Bits | Stop Bits   |

|-------|-----|-------------------|-------------|-------------|

| (1 b  | it) | (5to 9 data Bits) | (0 to 1bit) | (2bits 1to) |

**Figure 1.20**: Paquet UART [31].

#### I.2.12 PCI (Peripheral Component Interconnect) et PCI E (PCI Express)

Le bus PCI est un bus synchrone supportant un multiplexage de signaux d'adressages et de données. Il est avant tout prévu pour travailler avec des systèmes 32 bits, dans un fonctionnement en échange entre un maître et un esclave sous le contrôle d'un arbitre. [32]. La **Figure 1.21** représente l'architecture classique d'utilisation du bus PCI,

Figure 1.21: Schéma bloc d'une architecture PCI [32].

Le **Tableau 1.5** présente les caractéristiques paramètres de bus PCI, qui il existe deux paramètre essentiel caractérisant ces bus est la largeur du bus et la vitesse d'horloge :

| Variante PCI         | Vitesse<br>d'horloge | Largeur du bus |         | Débit de données<br>de pointe | Débit de données<br>pratique |

|----------------------|----------------------|----------------|---------|-------------------------------|------------------------------|

| PCI conventionnel    | 33 MHz               | 32 bits        | 4 bytes | 132 MB/s                      | 90 MB/s                      |

| uniquement           | 33 WITZ              | 64 bits        | 8 bytes | 264 MB/s                      | 180 MB/s                     |

| PCI conventionnel ou | 66 MHz               | 32 bits        | 4 bytes | 264 MB/s                      | 180 MB/s                     |

| PCI-X                | 00 WIIIZ             | 64 bits        | 8 bytes | 528 MB/s                      | 360 MB/s                     |

| PCI-X uniquement     | 133 MHz              | 32 bits        | 4 bytes | 532 MB/s                      | 360 MB/s                     |

|                      | 133 WIIIZ            | 64 bits        | 8 bytes | 1064 MB/s                     | 720 MB/s                     |

**Tableau 1.5 :** Caractéristiques du bus PCI [33].

Le transfert de données PCI peut être accompli à l'aide de "transferts burst" (voir la **Figure 1.22**). L'adresse et le type de transfert sont émis pendant la phase d'adressage, Un objet

de données (jusqu'à 32 bits (dans une implémentation 32 bits) ou 64 bits (dans une implémentation 64 bits) peut alors être transféré au cours de chaque phase de données subséquente [34]

Figure 1.22: Exemple de transfert du brust data [34].

Le PCI Express (Peripheral Component Interconnect Express) a remplacé anciens norme PCI. Il s'agit une série standard de bus d'extension pour connecter un ordinateur à un ou plusieurs dispositifs périphériques [35].

Le bus PCI Express se décline en plusieurs versions, 1X, 2X, 4X, 8X, 12X, 16X et 32X, permettant d'obtenir des débits compris entre 250 Mo/s et 8 Go/s. [36]. La **Figure 1.23** présente les quatre emplacements standards PCI express.

Figure 1.23: Quatre emplacements du PCIe standard [37].

#### I.2.13 USB (Universal serial bus) [38]

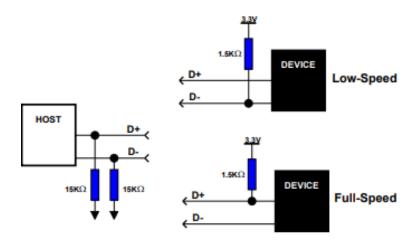

L'USB est une interface qui relie un appareil avec un ordinateur pour envoie et réception de données. La résistance pull-up (valeur de résistance est  $1.5 \mathrm{K}\Omega$ ) est placée sur la ligne D+ ou D- pour détecter la vitesse de l'appareil. La distance maximale du câble est de 25 mètre avec un débit maximal de 480 Mbits/s.

Si la ligne est D+: Indique que le périphérique connecté est un périphérique à vitesse maximum. Si la ligne est D-: Indique que le périphérique connecté est un périphérique à faible vitesse, comme représenté sur la **Figure I.24**. Le paquet de donnée est rapporté sur la **Figure 1.25**.

Figure 1.24: Détection de vitesse USB [38].

| Packet | Dir           | F | Sync     | SOF  | Frame | CRC5 | EOP        |

|--------|---------------|---|----------|------|-------|------|------------|

| 355    | $\rightarrow$ | S | 00000001 | 0×A5 | 951   | 0×13 | 250.000 NS |

**Figure 1.25 :** La trame USB [39].

Il existe 3 normes d'USB spécifiant la vitesse de transmission maximales, comme illustrées dans le **Tableau 1.6** [40].

**Tableau 1.6**: Vitesses de transmission maximales selon les différentes normes USB [40].

| Norme USB | Année | Vitesse de transmission maximale |

|-----------|-------|----------------------------------|

| USB 1.1   | 1998  | 12 Mbit/s                        |

| USB 2.0   | 2000  | 480 Mbit /s                      |

| USB 3.0   | 2009  | 4.8 Gbit/S (soit 600Mbits/s)     |

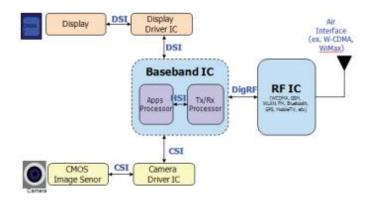

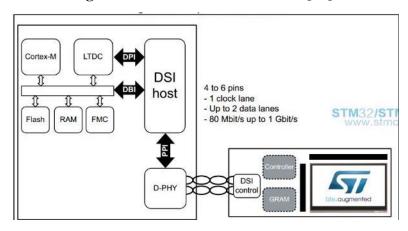

#### 1.2.14 CSI et DSI [41]

Avec l'inclusion d'écrans et de caméras haute résolution avec la possibilité de capturer ou de lire des vidéos haute définition, la quantité de transfert de données nécessaire pour atteindre cette haute définition a considérablement augmenté. L'interface (CSI-2) et l'interface série d'affichage (DSI) sont les deux protocoles de haut niveau basés sur des paquets qui transportent des données d'image entre le périphérique et le processeur d'application. Tous les deux utilisent la couche physique D-PHY. La **Figure 1.26** présente le schéma fonctionnel d'un appareil mobile typique.

Figure 1.26: Schéma fonctionnel d'un appareil mobile typique [41].

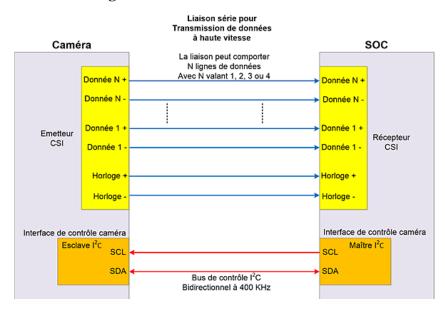

#### 1.2.14.1 CSI (Camera Serial Interface)[42]

C'est un bus série camera standard, défini par l'alliance MIPI (Mobile Industry Processor Interface). Il définit les bus reliant les différents composants embarqués dans les appareils mobiles comme l'illustrée la **Figure 1.27**.

Figure 1.27: Bus CSI du Raspberry PI [42].

#### 1.2.14.2 DSI (Display Serial Interface) [42]

C'est une spécification de l'alliance MIPI. Son objectif est de réduire le prix des écrans utilisés sur les mobiles. Sa structure est proche de celle du bus CSI, à l'exception près que les lignes de données partent du SoC et vont vers l'écran. La **Figure 1.28** suivante présente l'interface MIPI-DSI tandis qu'un exemple d'utilisation de l'interface DSI est présenté dans la **Figure 1.29**.

Figure 1.28: L'interface MIPI-DSI [43].

Figure 1.29: Exemple de l'interface DSI [43].

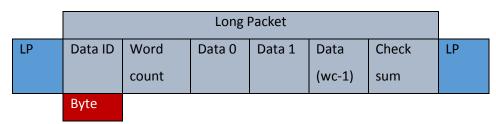

La communication au niveau des paquets est utilisée lors de l'envoi de données d'image à l'écran en format court (4 octets) ou long (6 à 65 541 octets). Les paquets longs et courts sont utilisés pour spécifier la taille des paquets, les données de paquets et l'erreur correction. Des paquets courts peuvent être envoyés pour des commandes qui ne nécessitent pas de données. Des paquets plus longs peuvent être utilisés pour envoyer des commandes avec plusieurs octets de données et de données d'image comme le montre la **Figure 1.30** [44].

|   | LP | Data | Data 0 | Data 1 | Error      | LP |

|---|----|------|--------|--------|------------|----|

|   |    | ID   |        |        | correction |    |

| • |    | Byte |        |        |            |    |

Figure 1.30: Niveau de paquet (paquets courts et longs) [44].

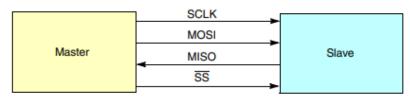

#### 1.2.15 SPI (Serial Peripheral Interface) [45]

Le SPI est un port d'entrée/sortie série synchrone à grande vitesse qui permet un bit série flux de longueur programmée (2 à 16 bits) à décaler entrée et sortie de l'appareil à un taux de transfert de bits programmé. Il est généralement utilisé pour communiquer entre l'appareil et les périphériques externes. Les applications typiques incluent une interface externe E/S périphérique ou extension via des périphériques tels que des registres de commutation, des pilotes d'affichage et SPI EPROMs et convertisseurs analogique-numérique.

Le bus d'interface périphérique série (SPI): La **Figure 1.31** montre comment le périphérique esclave est connecté au maître dans l'implémentation SPI maître unique, esclave unique et la **Figure 1.32** montre les implémentations SPI à maître unique et à esclaves multiples.

Figure 1.31: Implémentation SPI maître unique, esclave unique [46].

Figure 1.32: Mises en œuvre de plusieurs esclaves SPI [46].

Pour connecter le maitre et l'esclave on a quatre lignes de liaison. Le **Tableau 1.7** présente les lignes externes de ce bus.

| Lines and a Service (1.41). |                                                                                                   |  |  |  |  |  |

|-----------------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Signal                      | Description                                                                                       |  |  |  |  |  |

| SCLK                        | Signal d'horloge série avec la direction de l'appareil maître à esclave.                          |  |  |  |  |  |

| MOSI                        | Signal master-out/slave-in pour la transmission de données de maître à esclave en 8 bits, 12      |  |  |  |  |  |

|                             | bits, 16 bits, Largeur 20 bits, 24 bits ou 32 bits (sortie du maître).                            |  |  |  |  |  |

| MISO                        | Signal d'entrée/de sortie d'esclave pour la transmission de données d'esclave à maître en 8 bits, |  |  |  |  |  |

|                             | 12 bits, 16 bits, Largeur 20 bits, 24 bits ou 32 bits (sortie de l'esclave).                      |  |  |  |  |  |

| SS                          | Slave select signal, initiated by master to select slave device.                                  |  |  |  |  |  |

**Tableau 1.7:** Description des signaux [46].

# 1.2.16 SAS (Serial Attached SCSI), SATA (Serial Advanced Technology Attachment) 1.2.16.1 SATA (Serial Advanced Technology Attachment) [47]

Est une interface série full-duplex transmettre de donnée qui permet de connecté une carte mère avec nombreuse périphérique telle que disque dur et lecteur DVD) à technologie point à point qui peut prendre en charge plusieurs appareils mais il nécessite plusieurs linge [48]. **Trame SATA** se composent (Illustrée à la **Figure 1.33**): Un début de trame (SOF) délimité, Informations sur la couche de transport de charge utile, Contrôle de Redondance Cyclique (CRC), Un délimiteur de fin de trame (EOF). [47]

Figure 1.33 : Trame de donnée SATA [47].

La **Figure 1.34** présente les câbles à norme SATA.

**Figure 1.34:** Câbles SATA [47].

#### 1.2.16.2 SAS (Serial Attached SCSI)

C'est une interface matérielle standard pour les lecteurs de stockage. SAS est une architecture point à point qui utilise un contrôleur (adaptateur de bus hôte) avec deux canaux full-duplex qui fonctionnent simultanément. Chaque canal (port SAS) transfère les données à 3, 6 ou 12 Gbit/s dans chaque direction [48].

Les canaux SAS (ports) peuvent se connecter à un seul lecteur ou à un module d'extension qui connecte jusqu'à 128 lecteurs (ou adaptateurs de bus hôte). Un Fanout Expander peut connecter des Edge Expanders et un système peut prendre en charge 16 256 disques [48]. Le **Tableau 1.8** répertorie les débits de liaison physique pour SAS et SATA.

| Génération                         | Taux de liaison<br>physique | Bande passante pour 1 connexion | 4×Bande passante |

|------------------------------------|-----------------------------|---------------------------------|------------------|

| SAS-1,SAS-1,1,SATA Revision 1.0    | 1.5 Gbits/s                 | 150 MB/s                        | 600 MB/s         |

| SAS-1,SAS-1,1,SATA<br>Revision 2.0 | 3 Gbits/s                   | 300MB/s                         | 1200MB/s         |

| SAS-2,SAS-2,1,SATA<br>Revision 3.0 | 6 Gbits/s                   | 600 MB/s                        | 2400MB/s         |

**Tableau 1.8**: Taux de liaison physique par direction [49].

Les adresses utilisées dans SAS sont des unités 64 bits qui se composent de trois parties, comme Illustrées à la **Figure 1.35** [50] :

- Identifiant de 4 bits attribué par l'autorité d'adresse de nommage. Cette valeur est la même pour SAS et Fibre Channel, qui est de 5,

- Un identifiant d'entreprise 24 bits attribué par l'IEEE,

- Un identifiant spécifique au fournisseur de 36 bits.

**Figure 1.35 :** Adresse SAS [50].

#### Comparaison entre SAS et SATA:

Les disques SAS utilisent le même facteur de forme que Serial ATA (SATA) pour le connecteur de câble, mais ajoutent un deuxième port pour la connexion à deux contrôleurs ou extensions pour la tolérance aux pannes.

#### 1.2.17 IO-LINK:

IO-Link est une interface de communication point à point innovatrice pour le domaine des capteurs/actionneurs, spécifiée dans la norme CEI 61131-9[51]. La **Figure 1.36** montre la trame de donnée IO-Link et la séquence message.

Figure 1.36: Séquence de communication maître- Device IO-Link [52].

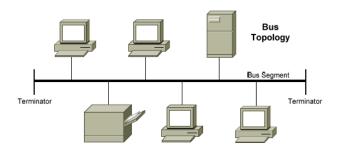

#### **1.2.18** Ethernet

C'est un protocole de communication série, de type topologies bus ou étoile, On utilise un câble pour relier les équipements informatique entre eux soit câble cuivre ou câble fibre optique. La longueur di câble varie entre 500 m à 20 km, avec un débit maximale de 40Gbits/s [53].

La **Figure I.37** présente le pochage de plusieurs équipements par le bus Ethernet tandis que la **Figure I.38** montre les bits circulés entre les terminaux.

Figure 1.37: Bus Ethernet [54].

| Preamble | SFD    | Destination address | Source address | Type    | Data          | CRC     |

|----------|--------|---------------------|----------------|---------|---------------|---------|

| 7 bytes  | 1 byte | 48 bits             | 48 bits        | 48 bits | 46-1500 bytes | 32 bits |

Figure 1.38: Paquet Ethernet [53].

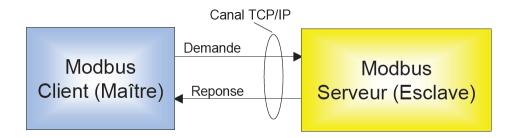

Le modèle de communication TCP/IP est illustré à la **Figure 1.39**.

Figure 1.39 : Le modèle de communication du TCP/IP.

#### 1.3 Conclusion

Dans ce chapitre, nous avons donné un aperçu général sur les protocoles de communication les plus utilisés en pratique. Dans le prochain chapitre, nous nous focalisons sur le protocole I2C qui sera implémenté sur une carte de développement, la DE1, afin de permettre le contrôle d'un codeur/décodeur audio.

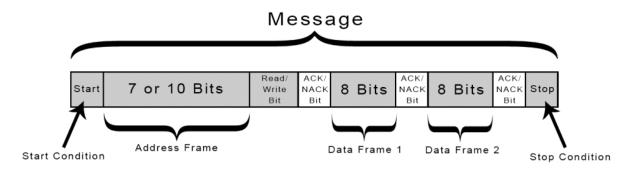

#### **II.1 Introduction**

Le bus I2C (Inter Integrated Circuit) a été développé au début des années 80 par Philips semi-conducators pour permettre de relier facilement à un microprocesseur les différents circuits d'un téléviseur moderne. Le bus I2C permet de faire communiquer entre eux des composants électroniques très divers grâce à seulement trois fils : Un signal de donnée (SDA), un signal d'horloge (SCL), et un signal de référence électrique (Masse). Ceci permet de réaliser des équipements ayants des fonctionnalités très puissantes (en apportant toute la puissance des systèmes micro programmés) et conservant un circuit imprimé très simple, par rapport à un schéma classique (8bits de données, 16 bits d'adresse+ les bits de contrôle).

Les données sont transmises en série à 100Kbits/s en mode standard et jusqu'à 400Kbits/s en mode rapide. Ce qui ouvre la porte de cette technologie à toutes les applications où la vitesse n'est pas primordiale. De nombreux fabricants ayant adopté le système, la variété des circuits disponibles disposant d'un port I2C est énorme : Ports d'E/S bidirectionnels, convertisseurs A/N et N/A, mémoires (RAM, EPROM, EEPROM, etc..), circuits audio (Equaliseur, Contrôle de volume, ...) et autre drivers (LED, LCD, ...). Le nombre de composants qu'il est ainsi possible de relier est essentiellement limité par la charge capacitive des lignes SDA et SCL : 400 pF.

#### II.2. Le bus de communication I2C

L'objectif est de permettre la communication entre plusieurs équipements. Il existe une très grande variété de bus de communication car aucun bus n'est universel. Il faut choisir le bus en fonction de [55]:

- > Distance entre les équipements (cm, m, km),

- Nombre d'équipements à relier,

- > Débit de données (contrôle ou data),

- Consommation autorisée (pile/secteur),

- > Stabilité nécessaire (bruit),

- > Catalogue disponible,

- Cout (en générale, la bonne solution est trop chère).

La structure du bus I2C est illustrée sur la Figure 2.1.

**Figure 2.1**: Bus I2C [56].

#### II.2.1 Etude du bus I2C

Le bus I2C permet de faire communiquer entre des composants électroniques grâce à trois fils (**Figure 2.2**) :

- Signal de données SDA,

- ➤ Signal d'horloge SCL,

- > Signal de référence électrique GND (masse).

Le **Tableau 2.1** reporte les caractéristiques principales du bus I2C.

Tableau 2.1 : Les caractéristiques du bus I2C.

| Fils utilisés             | 2                           |  |  |

|---------------------------|-----------------------------|--|--|

| Vitesse maximum           | Mode standard =100Mbps      |  |  |

|                           | Mode rapide=400Kbps         |  |  |

|                           | Mode Grande vitesse=3,4Mbps |  |  |

|                           | Mode ultra rapide=5Mbps     |  |  |

| Synchrone ou asynchrone ? | Synchrone                   |  |  |

| Série ou parallèle        | Série                       |  |  |

| Max #of Masters           | Illimitée                   |  |  |

| Max #of Slaves            | 1008                        |  |  |

Figure 2.2: Structure d'E/S d'un module I2C [57].

# II.3 Le protocole I2C

Le protocole I2C définit la succession des états logiques possibles sur SDA et SCL et la façon dont doivent réagir les circuits en cas de conflits.

#### II.3.1 Glossaire I2C

Le **Tableau 2.2** résume le glossaire I2C.

Tableau 2.2 : Glossaire I2C [58].

| Abonné    | Tout élément connecté sur le bus                                                              |  |

|-----------|-----------------------------------------------------------------------------------------------|--|

| Emetteur  | Tout abonné qui envoie des données sur SDA                                                    |  |

| Récepteur | Tout abonné qui reçoit des données de SDA                                                     |  |

| Maître    | Tout abonné qui démarre et termine un échange. Le maître place l'horloge sur SCL              |  |

| Esclave   | Tout abonné adressé par un maitre. Un esclave a la possibilité d'arrêter l'horloge du maitre. |  |

| Adresse   | Numéro attribué à un esclave. Sur le bus tous les esclaves ont une adresse unique             |  |

| Echange   | Dialogue entre un maitre et un esclave                                                        |  |

| Arbitrage | Résolution du conflit d'un accès simultané par 2 maitres.                                     |  |

#### II.3.2. Câblage I2C

Les lignes SCL et SDA sont par défaut à VDD. Pour mettre 1 sur SCL ou SDA, un abonné programme le port en entrée, la résistance Rp se charge de tirer la ligne à 1. Pour mettre 0 sur SCL ou SDA, un abonné doit écrire un 0, c.-à-d. relier la ligne à la masse. Il ne peut jamais y avoir de conflit électrique (court-circuit VDD-GND) comme le montre la **Figure 2.3**.

**Figure 2.3:** Câblage I2C [59].

#### II.3.3. La prise de contrôle du bus I2C

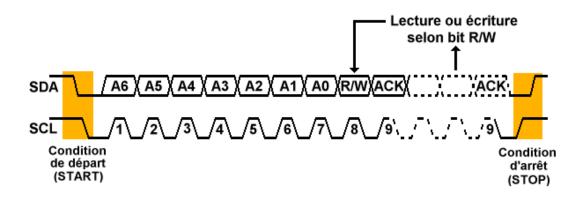

Pour prendre le contrôle du bus, il faut que celui-ci soit au repos (SDA et SCL à '1'). Pour transmettre des données sur le bus, il faut donc surveiller deux conditions particulières [55]:

- La condition de départ (SDA passe à '0' alors que SCL reste à 1 )

- La condition d'arrêt (SDA passe à '1' alors que SCL reste à '1')

Lorsqu'un circuit, après avoir vérifié que le bus est libre, prend le contrôle de celui-ci, il en devient le maître. C'est lui qui génère le signal d'horloge. Un schéma décrivant la condition de départ et d'arrêt est illustré à la **Figure 2.4**.

Figure 2.4: Condition de départ et d'arrêt [60].

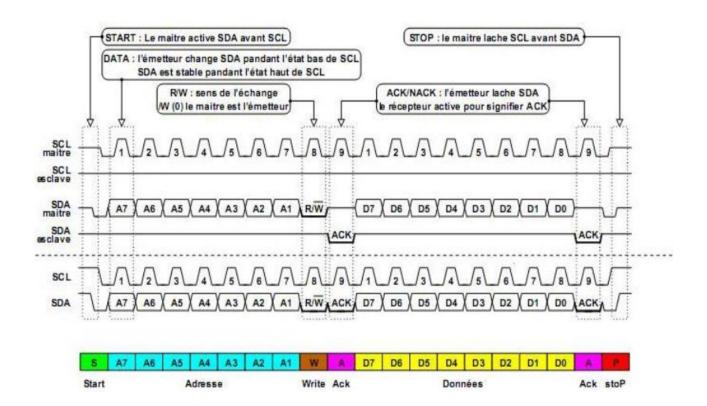

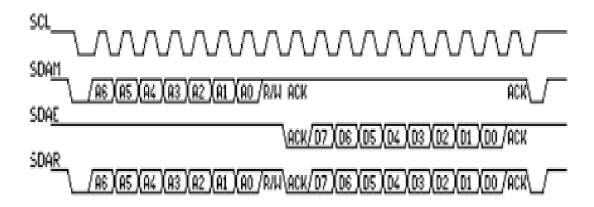

#### II.3.4. Ecriture d'un octet (une donnée) [61]

Avant de placer les bits qui forment l'octet à transmettre sur le bus, le maître doit placer la ligne d'horloge SCL à 0. Tant que la ligne SCL est au niveau haut, la ligne SDA ne doit pas changer d'état, sinon cette condition sera interprétée comme la condition d'arrêt. Celle-ci peut survenir même au milieu de la transmission d'un octet, pour abandonner la transmission et libérer le bus pour les autres circuits. Pour transmettre correctement les bits sur la ligne SDA, le maître doit donc tout d'abord placer la ligne SCL à 0. Ensuite, le maître peut placer la ligne SDA au niveau correspondant au bit à transmettre et replacer la ligne SCL au niveau 1 pour indiquer que le bit est présent sur la ligne SDA. La même opération va se répéter autant de fois que nécessaire pour transmettre les 8 bits de données. Notez que c'est le bit de poids fort qui est transmis en premier.

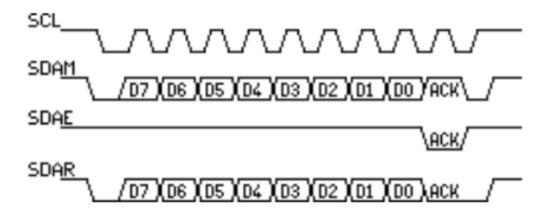

Une fois les 8 bits transmis, le circuit qui vient de recevoir les données doit imposer un bit d'acquittement ACK sur la ligne SDA. Pour cela, pendant que la ligne SCL est au niveau bas, le maître place sa propre sortie au niveau haut, tandis que le récepteur (aussi appelé l'esclave) place sa sortie au niveau bas. Puisque les sorties sont à collecteur ouvert, la ligne SDA restera au niveau bas à cause de l'esclave. Le maître relit ensuite la ligne SDA une fois qu'il a passé la ligne SCL au niveau haut. Si la valeur lue pour le bit ACK est 0, c'est que l'esclave s'est bien acquitté de l'octet reçu, sinon c'est qu'il y a une erreur et le maître doit générer la condition arrêt. Un exemple d'une transmission réussie est représenté sur la **Figure 2.5**. Les étapes d'écriture d'un octet sont reportées sur la **Figure 2.6**.

Figure 2.5 : Exemple de transmission réussie [62].

#### Dans cet exemple:

> SCL : Horloge imposée par le maître

> SDAM : Niveaux de SDA imposés par le maître

> SDAE : Niveaux de SDA imposés par l'esclave

> SDAR : Niveaux de SDA réels résultants

Figure 2.6: Trame de base : Ecriture d'un octet [63].

#### II.3.5. Transmission d'une adresse[63]

Le nombre de composants qu'il est possible de connecter sur un bus I2C étant largement supérieur à deux, il est nécessaire de définir pour chacun une adresse unique. L'adresse d'un circuit, codée sur sept bits, est définie d'une part par son type et d'autre part par l'état appliqué à un certain nombre de ces broches. Cette adresse est transmise sous la forme d'un octet au format particulier comme l'explique la **Figure 2.7** suivante.

**Figure 2.7:** Exemple d'octet d'adresse [64].

On remarque ici que les bits D7 à D1 représentent les adresse A6 à A0, et que le bit D0 et remplacé par le bit de R/W qui permet au maître de signaler s'il veut lire ou écrire une donnée. Le bit d'acquittement ACK fonctionne comme pour une donnée, ceci permet au maître de vérifier si l'esclave est disponible.

#### Note 1: Cas particuliers des mémoires

L'espace adressable d'un circuit de mémoire étant sensiblement plus grand que la plupart des autres types de circuits, l'adresse d'une information y est codée sur deux octets ou plus. Le premier représente toujours l'adresse du circuit, et les suivants l'adresse interne de la mémoire.

#### Note 2 : Les adresses réservées

Les adresses 00000XXX et 111111XX sont réservés à des modes de fonctionnement particuliers.

#### Note 3: Cas particulier d'utilisation d'ACK

L'écriture d'un octet dans certains composants (Mémoires, microcontrôleur......) peut prendre un certain temps. Il est donc possible que le maître soit obligé d'attendre l'acquittement ACK avant de passer à la suite[63].

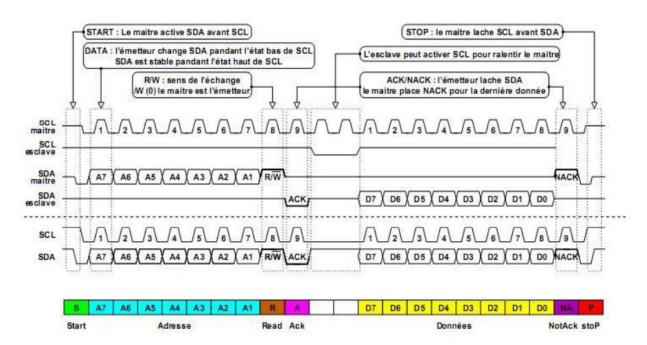

#### II.3.6. Lecture d'une donnée

La lecture d'une donnée par le maître se caractérise par l'utilisation spéciale qui est faite du bit ACK. Après la lecture d'un octet, le maître positionne ACK à '0' s'il veut lire la donnée suivante (cas d'une mémoire par exemple) ou à '1' (cas échéant). Il envoie alors la condition d'arrêt[12]. La **Figure 2.8** illustre un exemple de lecture d'une donnée tandis que la **Figure 2.9** décrit la trame de base en état d'attente.

Figure 2.8 : Exemple de lecture d'une donnée [65].

**Figure 2.9 :** Trame de base : Etat d'attente [66].

#### II.4 Utilisation de l'I2C